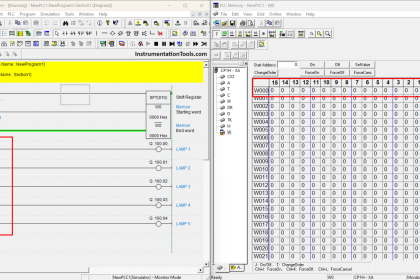

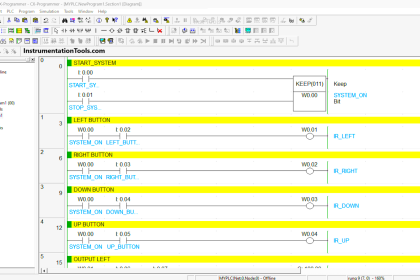

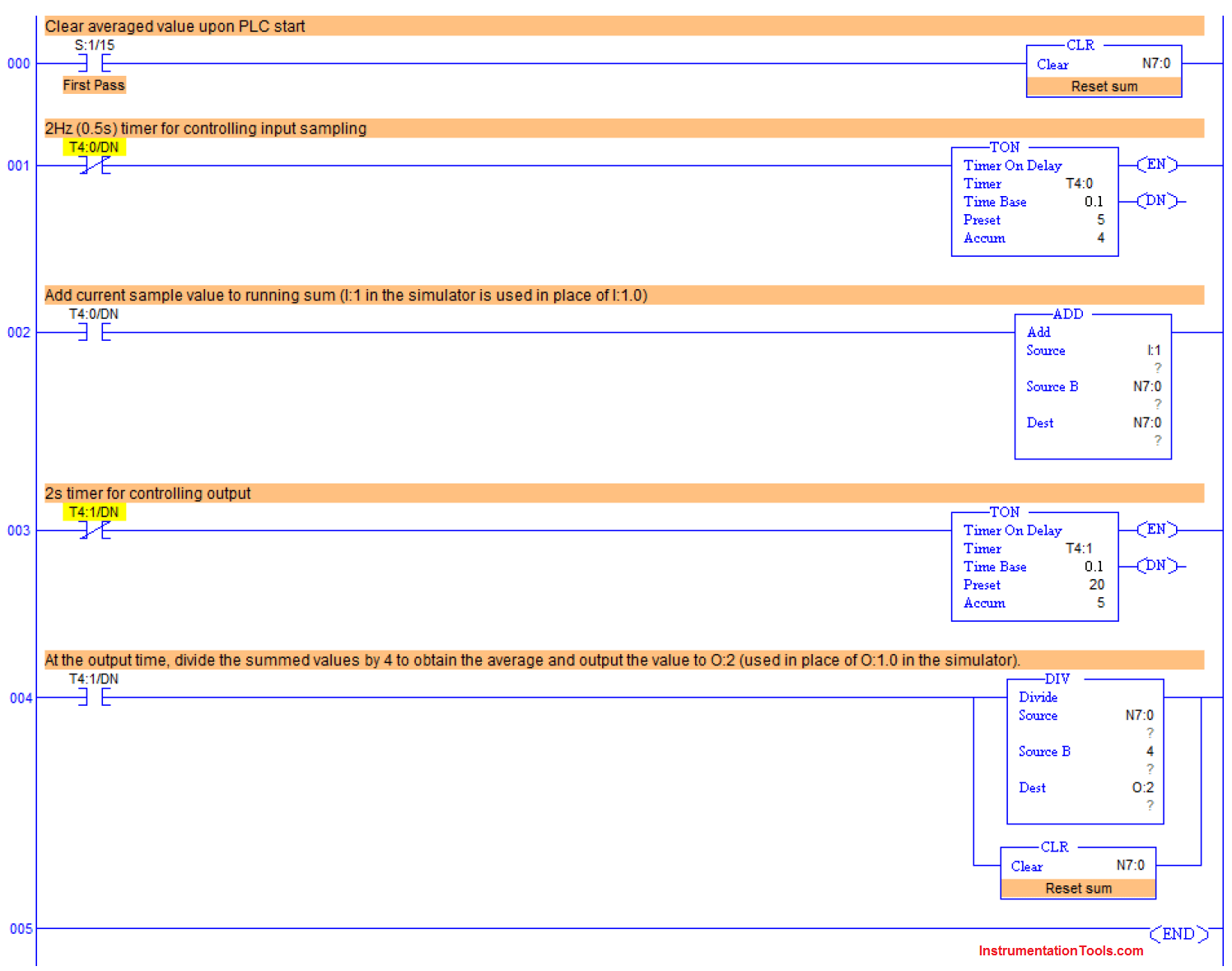

Design an efficient PLC ladder logic program that samples analog input (I:1.0) at the rate of 2Hz and outputs the average value to analog output O:1.0 once every two seconds.

PLC Analog Input Sampling Ladder Logic

You can share the detailed explanation of above PLC ladder logic with comments section.

Author: Dr. D. J. Jackson

If you liked this article, then please subscribe to our YouTube Channel for PLC and SCADA video tutorials.

You can also follow us on Facebook and Twitter to receive daily updates.

Read Next:

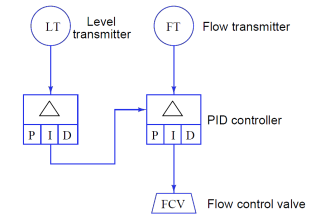

- DCS and PLC Flow Diagram

- Logic Gates and Truth tables

- Siemens PLC Maths Instructions

- Two out of Three Logic Analogy

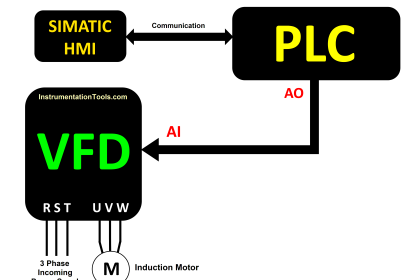

- Motor Speed Control with PLC