Digital Ramp Analog to Digital Converter (ADC) also known as the stair-step-ramp, or simply counter A/D converter, this is also fairly easy to understand but unfortunately suffers from several limitations.

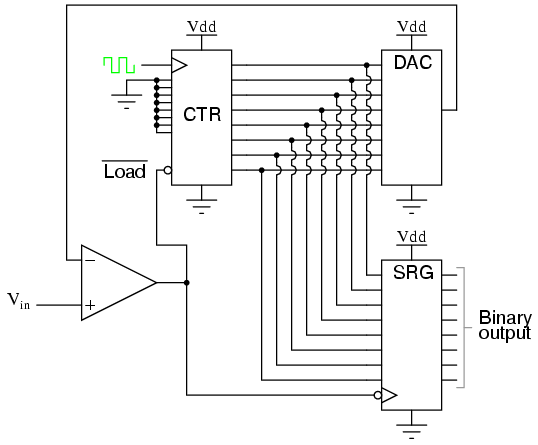

The basic idea is to connect the output of a free-running binary counter to the input of a DAC, then compare the analog output of the DAC with the analog input signal to be digitized and use the comparator\’s output to tell the counter when to stop counting and reset. The following schematic shows the basic idea:

As the counter counts up with each clock pulse, the DAC outputs a slightly higher (more positive) voltage. This voltage is compared against the input voltage by the comparator. If the input voltage is greater than the DAC output, the comparator\’s output will be high and the counter will continue counting normally.

Eventually, though, the DAC output will exceed the input voltage, causing the comparator\’s output to go low. This will cause two things to happen: first, the high-to-low transition of the comparator\’s output will cause the shift register to “load” whatever binary count is being output by the counter, thus updating the ADC circuit\’s output; secondly, the counter will receive a low signal on the active-low LOAD input, causing it to reset to 00000000 on the next clock pulse.

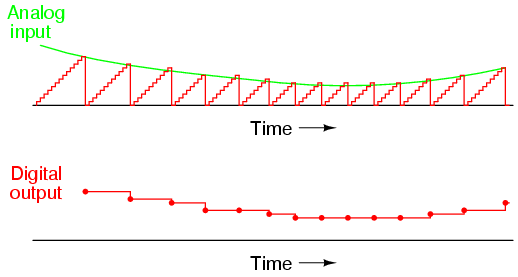

The effect of this circuit is to produce a DAC output that ramps up to whatever level the analog input signal is at, output the binary number corresponding to that level, and start over again. Plotted over time, it looks like this:

Note how the time between updates (new digital output values) changes depending on how high the input voltage is. For low signal levels, the updates are rather close-spaced.

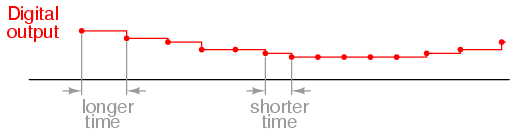

For higher signal levels, they are spaced further apart in time:

For many ADC applications, this variation in update frequency (sample time) would not be acceptable.

This, and the fact that the circuit\’s need to count all the way from 0 at the beginning of each count cycle makes for relatively slow sampling of the analog signal, places the digital-ramp ADC at a disadvantage to other counter strategies.